Multiplexer 란?

멀티플렉서의 정의

멀티플렉서(MUX)는 여러 개의 입력 신호 중 하나를 선택하여 단일 출력 신호로 전달하는 논리 회로이다.

멀티플렉서는 다양한 디지털 시스템에서 사용되며, 선택 기능을 효율적으로 수행한다.

멀티플렉서의 구성

- 정보 입력 ($I0, I1, ..., I_{2^n - 1}$): 멀티플렉서는 (2^n)개의 정보 입력을 가질 수 있다. 이 중 하나가 선택되어 출력한다.

- 제어 입력 (선택 입력, $S_{n-1}, … S0$): n개의 제어 입력은 Select Lines을 의미하며, 어떤 정보 입력이 출력될지를 결정한다.

- 출력 (Y): 선택된 정보 입력이 출력으로 전달

멀티플렉서의 동작 원리와 활용

멀티플렉서는 제어 입력(선택선)에 따라 특정 정보 입력을 선택하고, 이를 단일 출력으로 전달한다.

예를 들어, 2개의 제어 입력(Select Lines)을 가지는 4:1 멀티플렉서의 경우, 4개의 정보 입력 중 하나를 선택하여 출력한다.

제어 입력 신호가 2 비트인 경우 4가지 경우의 수 (00, 01, 10, 11)에 따라 4가지 조합이 가능하기 때문.

따라서 제어 입력 신호 n비트는 입력 신호 $2^n$개를 표현할 수 있다.

멀티플렉서는 다양한 디지털 회로와 시스템에서 활용된다.

특히, CPU 내부에서 다양한 데이터 소스에서 하나를 선택하여 명령어를 실행하는 데 사용되며,

조건문(if 또는 case) 구현에도 사용된다.

Multiplexer 설계

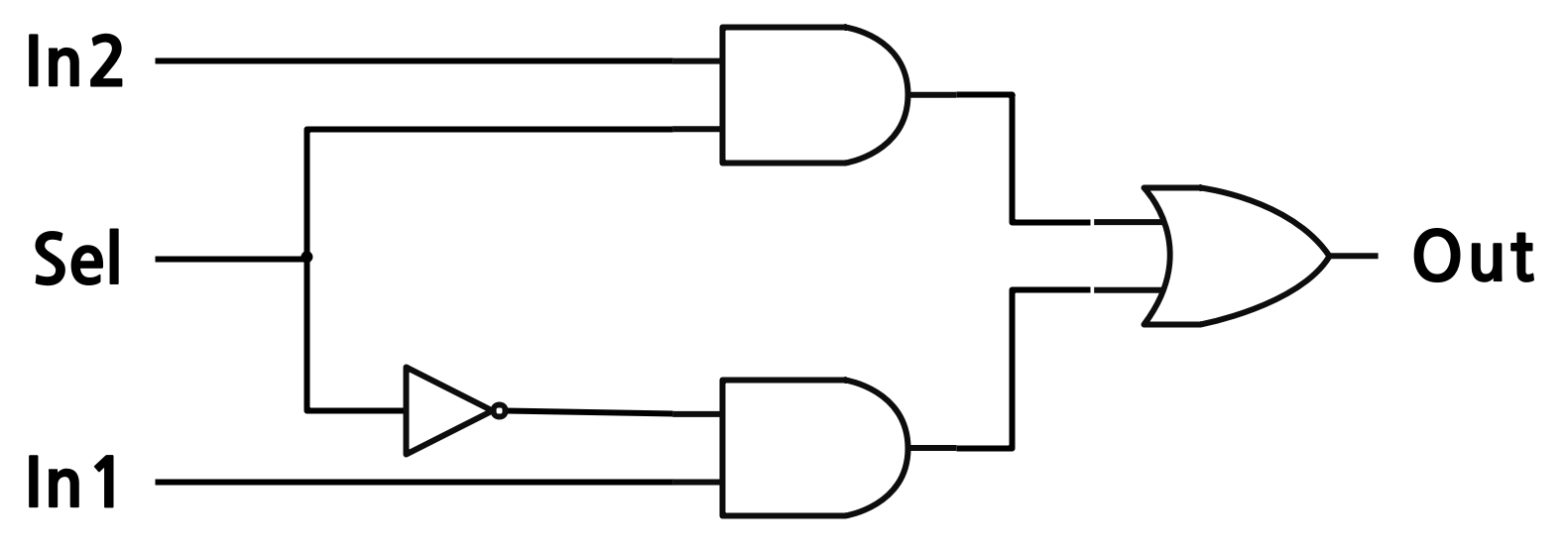

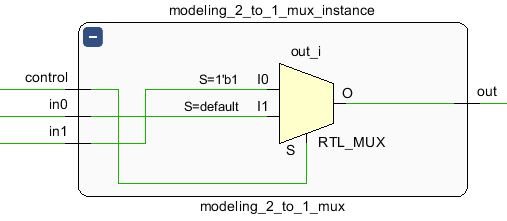

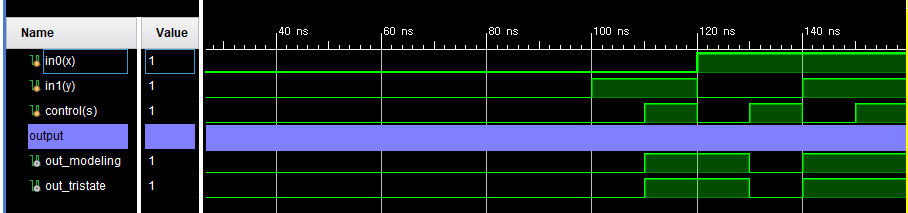

2:1 MUX

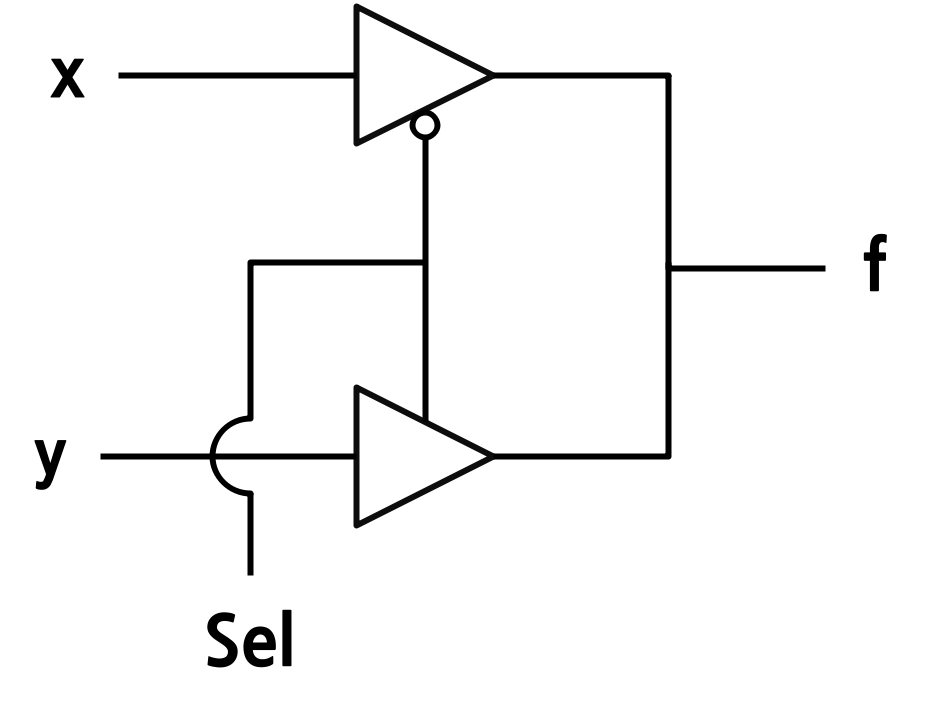

위 그림들은 다양한 방식으로 구현한 2 : 1 MUX의 회로도이다.

제어 신호(Sel)는 1 비트이므로, 선택 가능한 입력 신호의 개수는 $2^1 = 2$로 2개이다.

방정식은 $Y = \bar {S}I_0 + SI_1 $ 로 나타낼 수 있다.

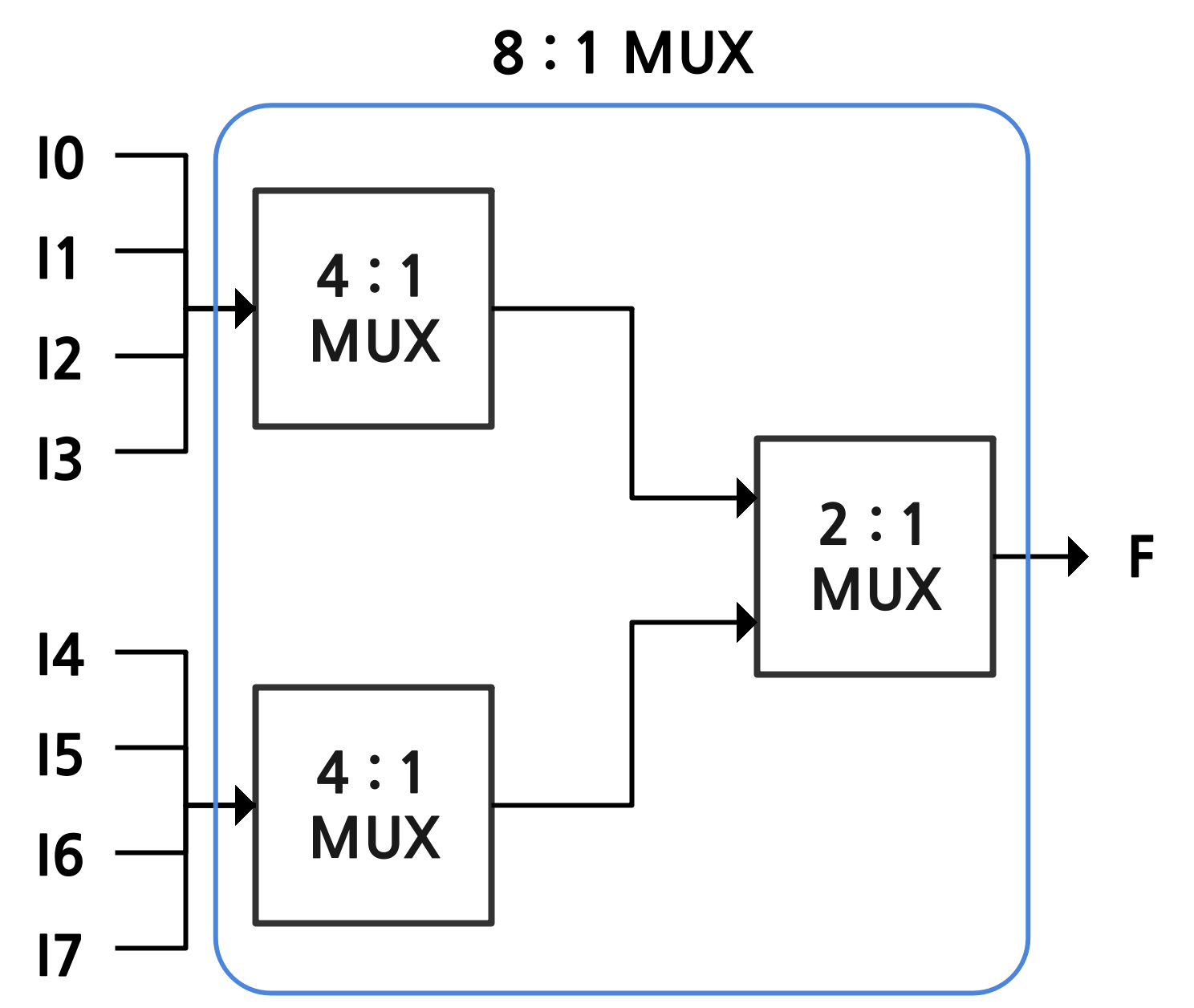

Multiplexer의 확장

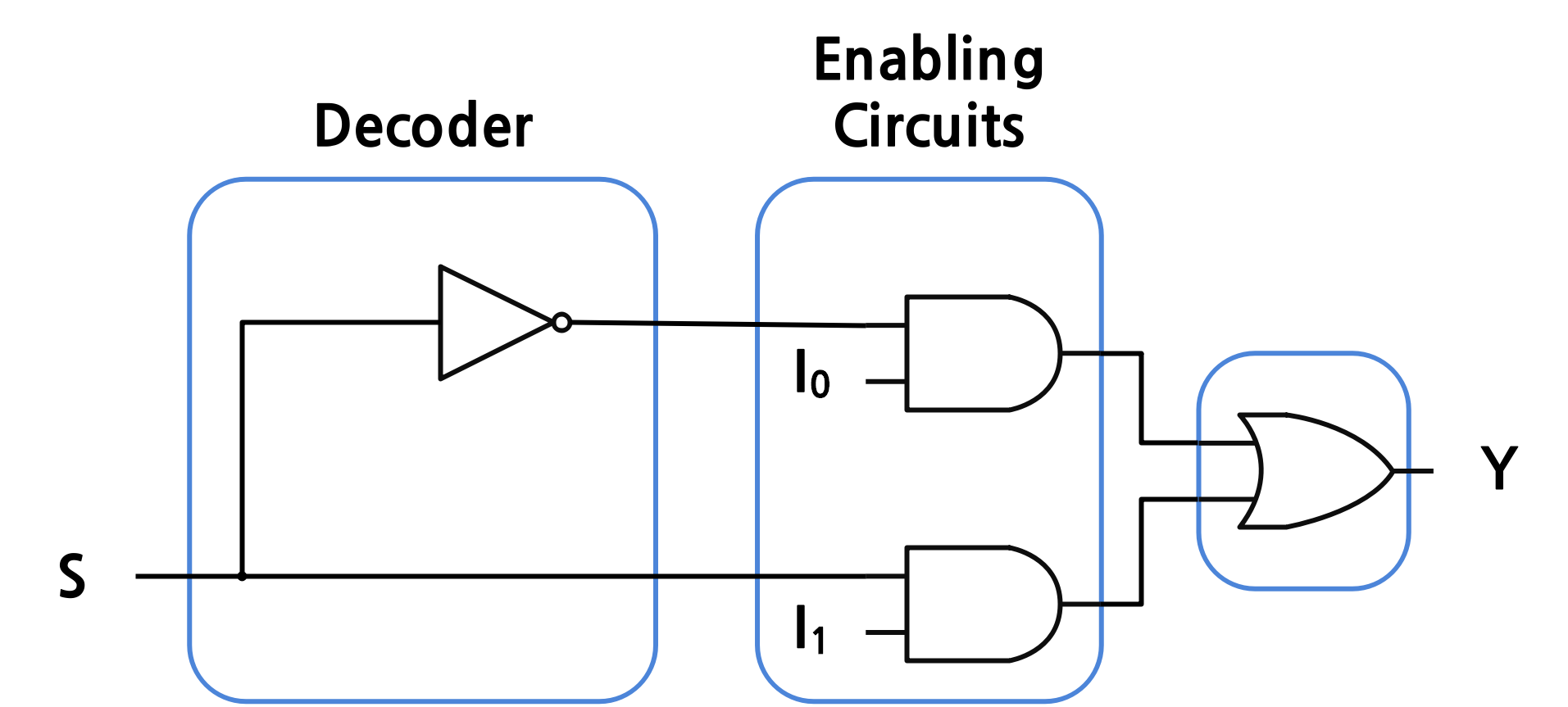

위 사진을 보면 2:1 Line Multiplexer가 다음과 같이 구성되는 점을 확인할 수 있다.

- 1-to-2 Line Decoder

- 2 Enabling circuits

- 2-input OR gate

여기서 Multiplexer의 확장을 위한 설명

- 1-to-2 Line Decoder : 입력이 1개인 Decoder를 사용하여 2개의 출력 라인 중 하나를 활성화한다.

- 2개의 1 x 2 AND-OR 회로 : Decoder의 두 출력은 각각의 AND 게이트에 입력되어 출력 신호를 생성하고 OR 게이트를 통해 최종 출력ㅇ으로 결합된다.

- $2^n$-to-1 Multiplexer

- n-to- $2^n$ Decoder : n개의 입력 비트를 사용하여 $2^n$개의 출력 라인 중 하나를 선택한다.

- $2^n$ x 2 AND-OR 회로: 각 출력 라인에 대해 AND 게이트와 OR 게이트를 사용하여 최종 출력을 생성한다.

이와 같은 방식으로 멀티플렉서의 확장이 이루어진다.

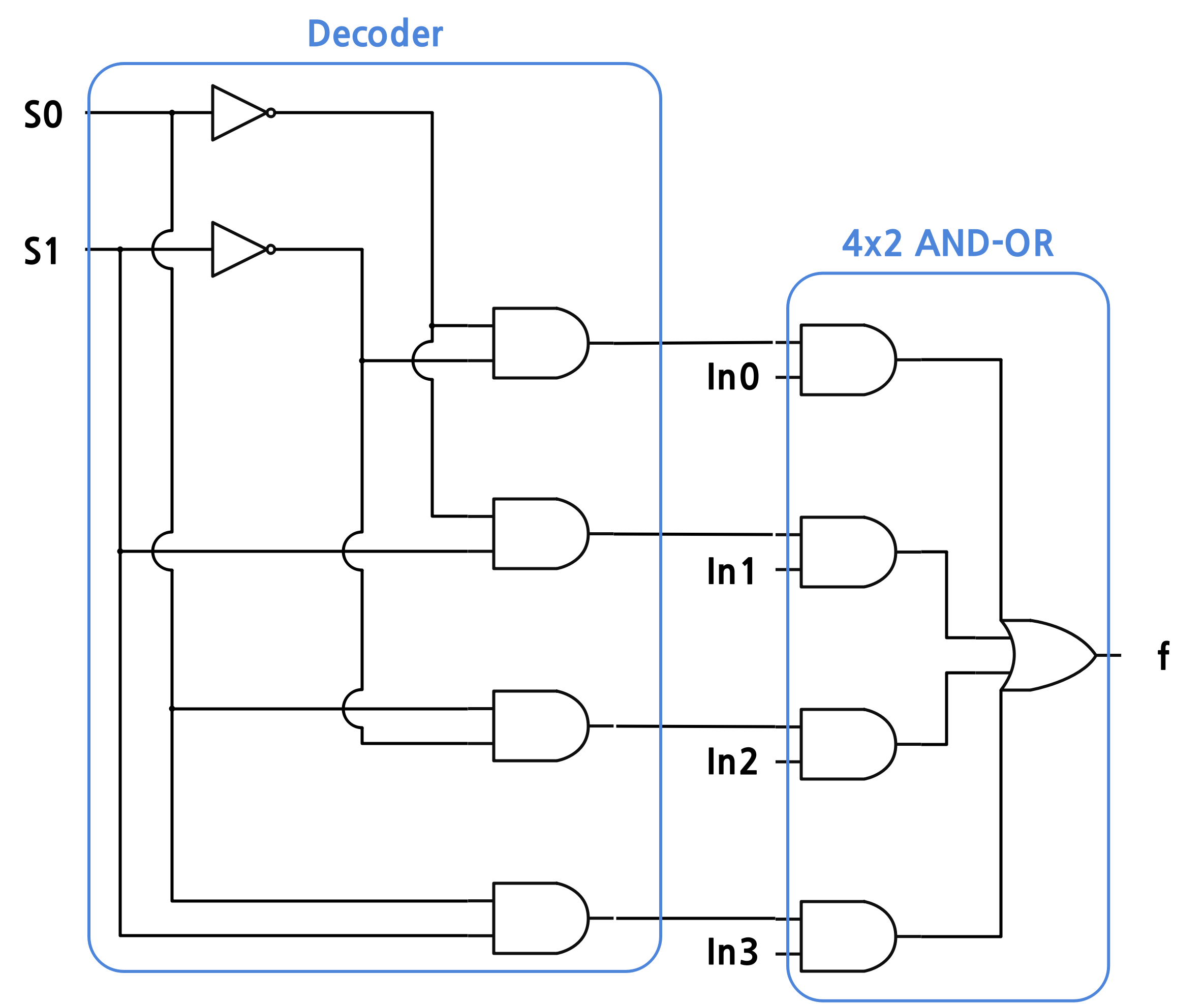

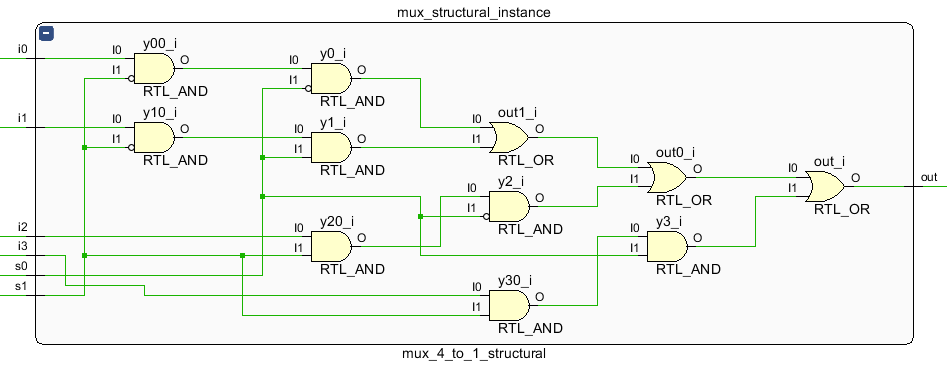

4:1 MUX

위에서 설명했던 Multiplexer의 확장 방식으로 Decoder와 AND-OR 회로를 이용하여 4-to-1 MUX로 확장할 수 있음을 확인할 수 있다.

4개의 정보 입력(In0, In1, In2, In3)과 2개의 제어 입력(S0, S1)을 가진다.

제어 입력에 따라 4개의 정보 입력 중 하나가 선택되어 출력으로 전달된다.

2:1 MUX 설계 코드

// 2-to-1 multiplexer using conditional operator

assign out = control ? in1 : in0; // If control is 1, out = in1; if control is 0, out = in0

// tristate 2-to-1 mux

bufif0 b1 (f, x, s);

bufif1 b2 (f, y, s);

4:1 MUX 설계

module mux_4_to_1_structural(

input i0, i1, i2, i3, s1, s0,

output out

);

wire s1n, s0n; // Internal wire

wire y0,y1,y2,y3;

// Gate instantiations

not (s1n, s1);

not (s0n, s0);

and (y0, i0, s1n, s0n);

and (y1, i1, s1n, s0);

and (y2, i2, s1, s0n);

and (y3, i3, s1, s0);

or (out, y0, y1, y2, y3);

endmodule

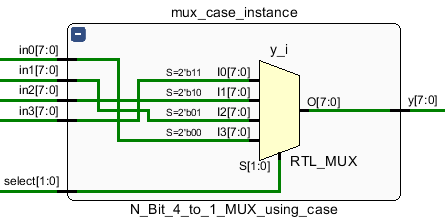

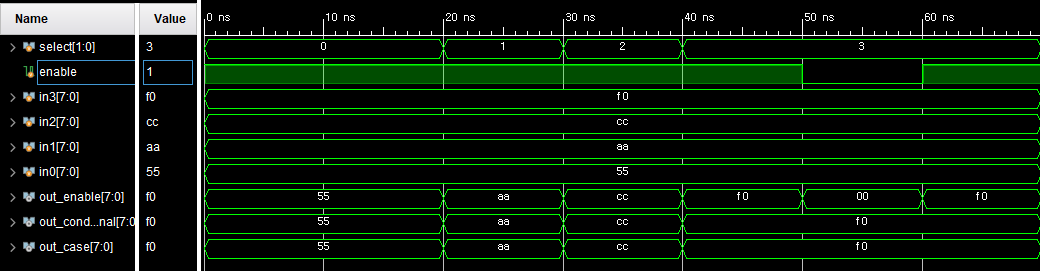

N:1 MUX 설계

// N-bit 4-to-1 multiplexer using conditional operator

assign y = select[1] ?

(select[0] ? in3 : in2) :

(select[0] ? in1 : in0);

Demultiplexer 란?

Demultiplexer의 개념과 구조

Demultiplexer(디멀티플렉서, Demux)는 이름에서 알 수 있듯 Multiplexer의 반대로 동작하는 논리 회로이다.

즉, 하나의 입력 신호를 여러 개의 출력 신호로 분배하는 장치다.

Demux는 선택 신호(Select Lines)를 이용해 입력 신호를 특정 출력으로 보내는 방식으로 동작한다.

선택 신호가 2비트인 경우 4가지 경우의 수 (00, 01, 10, 11)에 따라 입력 신호를 4개의 출력 중 하나로 보낸다.

구조는 다음과 같다.

- 입력 : 하나의 디지털 신호

- 선택 신호 : n비트 신호, $2^n$개의 출력 신호를 표현할 수 있다.

- 출력: 여러 개의 출력 신호

Demultiplexer 설계

always @(*) begin

if (select == 3) y3 = in; else y3 = 1'b0;

if (select == 2) y2 = in; else y2 = 1'b0;

if (select == 1) y1 = in; else y1 = 1'b0;

if (select == 0) y0 = in; else y0 = 1'b0;

end

'Verilog-Basic' 카테고리의 다른 글

| Encoder/Decoder 설계 (0) | 2024.07.13 |

|---|---|

| ALU(Arithmetic Logic Unit, 산술 논리 연산 장치) - ALU 74181 설계 (0) | 2024.07.11 |

| Carry-Lookahead Adder 설계 (0) | 2024.07.09 |

| Ripple Carry Adder (리플 캐리 가산기), n bit full adder 설계 (0) | 2024.07.09 |

| 1-Bit half adder, full adder (반가산기, 전가산기 설계) (0) | 2024.07.09 |