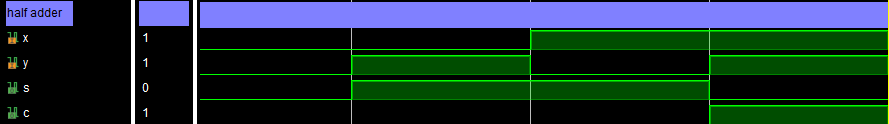

반가산기 half adder

반가산기는 두 개의 1비트 이진수를 더하여 합(Sum)과 자리올림(Carry)을 생성한다.

- 합( Sum ): 입력 A와 B의 XOR 결과

- 자리올림( Carry ): 입력 A와 B의 AND 결과

반가산기 진리표

| Input A | Input B | 합 (Sum) | 자리올림 (Carry) |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

반가산기 verilog 설계

// Half Adder Module

module half_adder(

input wire x, y, // Input bits

output wire s, c // Sum and carry outputs

);

// XOR gate for sum calculation

xor xor1(s, x, y);

// AND gate for carry calculation

and and1(c, x, y);

endmodule

전가산기 full adder

전가산기는 세 개의 1비트 이진수를 더한다. 반가산기 두 개와 OR 게이트로 구성된다.

- 첫 번째 반가산기: 입력 A와 B를 더하여 중간 합과 중간 자리올림을 생성

- 두 번째 반가산기: 첫 번째 반가산기의 합과 자리올림 입력을 더하여 최종 합과 최종 자리올림을 생성

- 최종 자리올림: 두 반가산기의 자리올림을 OR 게이트로 결합하여 생성

전가산기 진리표

| Input A | Input B | Input Cin | Sum | Cout |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

전가산기 verilog 설계

// Full Adder Module using Structural Modeling

module full_adder_structural(

input wire x, // First input bit

input wire y, // Second input bit

input wire c_in, // Carry input bit

output wire sum, // Sum output bit

output wire c_out // Carry output bit

);

// Internal wires to connect the half adders

wire s1, c1, c2;

// First Half Adder Instance

// Adds x and y, producing a sum (s1) and a carry (c1)

half_adder HA2( .x(c_in), .y(s1), .s(sum), .c(c2) );

// Second Half Adder Instance

// Adds carry input (c_in) and the sum from the first half adder (s1)

// Produces the final sum and an intermediate carry (c2)

half_adder HA2( .x(c_in), .y(s1), .s(sum), .c(c2) );

// OR Gate to produce the final carry out (c_out)

// Combines the carry outputs from both half adders (c1 and c2)

or or1( .c_out(c_out), .c1(c1), .c2(c2) );

endmodule

Structural modeling 이외의 Dataflow, Behavioral modeling, testbench code는 아래 링크에서 다운 및 조회

'Verilog-Basic' 카테고리의 다른 글

| Encoder/Decoder 설계 (0) | 2024.07.13 |

|---|---|

| ALU(Arithmetic Logic Unit, 산술 논리 연산 장치) - ALU 74181 설계 (0) | 2024.07.11 |

| Multiplexer (MUX, 멀티플렉서)/Demultiplexer(Demux) 설계 (0) | 2024.07.10 |

| Carry-Lookahead Adder 설계 (0) | 2024.07.09 |

| Ripple Carry Adder (리플 캐리 가산기), n bit full adder 설계 (0) | 2024.07.09 |